Ilaria Scarabottolo

I am a post-doc researcher at Università della Svizzera italiana (Lugano, Switzerland), in the research group led by Prof. Laura Pozzi. I am curious and interested about everything related to applied Mathematics, my education and life choices brought me to the fascinating field of Approximate Computing and, in particular, to the design of approximate hardware for error-tolerant applications. My research work has mostly focused on logic simplification for the design of approximate, energy-efficient circuits, and on the development of algorithms to derive error models of faulty hardware without needing any a-priori knowledge of the given application. I have also worked on fault-detection in distributed systems and signal processing, mainly during my master thesis at Politecnico di Milano (Italy). More recently, I have also approached the boolean satisfiability problem applied to logic simplification for approximate circuits, as well as the study of stochastic error derivation and propagation in approximate hardware.

Research

Since the beginning of my school career I have been attracted to engineering subjects and to the idea of contributing to a sustainable and efficient technological development. My research direction stems from this deep interest and lands in the field of Approximate Computing, a rising computing paradigm that promotes informed trade-offs between energy efficiency and accuracy. Indeed, a vast number of applications do not need fully-precise computations to produce satisfying results. A few of many examples are media processing applications, where a small quality loss can be afforded due to the impossibility for human users to perceive it; wireless sensor networks, where data can be already corrupted due to noise and redundant acquisitions; recommender systems that do not have a single golden answer; heuristic and probabilistic algorithms that deal with average values and do not even aim at obtaining fully precise results.

On the other hand, the majority of those applications is power-hungry and energy consumption has to be carefully controlled.

Indeed, a vast number of applications do not need fully-precise computations to produce satisfying results. A few of many examples are media processing applications, where a small quality loss can be afforded due to the impossibility for human users to perceive it; wireless sensor networks, where data can be already corrupted due to noise and redundant acquisitions; recommender systems that do not have a single golden answer; heuristic and probabilistic algorithms that deal with average values and do not even aim at obtaining fully precise results.

On the other hand, the majority of those applications is power-hungry and energy consumption has to be carefully controlled.

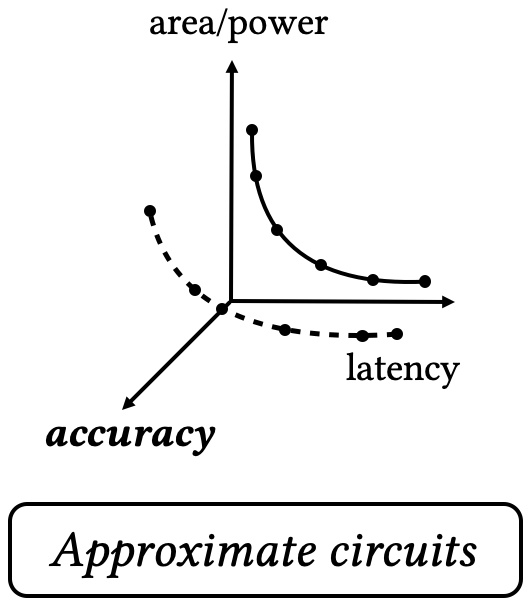

My research project aims at obtaining energy-efficient inexact circuits, starting from their exact counterparts and given an error level tolerance. These hardware components can be employed in any error-resilient application, entailing remarkable gains in energy savings by slightly reducing the accuracy level.

During my PhD, I have focused on developing algorithms to automatically synthesize such circuits, without needing a-priori knowledge of the specific problem. Along with identifying most efficient faulty circuits, I have studied methodologies to derive error-models for circuits or larger systems, such as Neural Netwok or FPGAs. I am currently working on integrating probabilistic analysis to such algorithms, since they represent an interesting and valid opportunity to further improve energy efficiency. Finally, I am also exploring different ways of approaching error-modeling problems, by expressing them in form of satisfiability problems.

Publications

Approximate Logic Synthesis: a Survey

A comprehensive survey of the most popular Approximate Logic Synthesis techniques. These tecnhinques are divided into categories and briefly illustrated highlighting their strengths and weaknesses. Finally, we have evaluated their efficiency by comparing their performance on arithmetic circuits approximation, outlining which strategies lead to the most efficient approximate designs.

Partition and Propagate: an Error Derivation Algorithm for the Design of Approximate Circuits

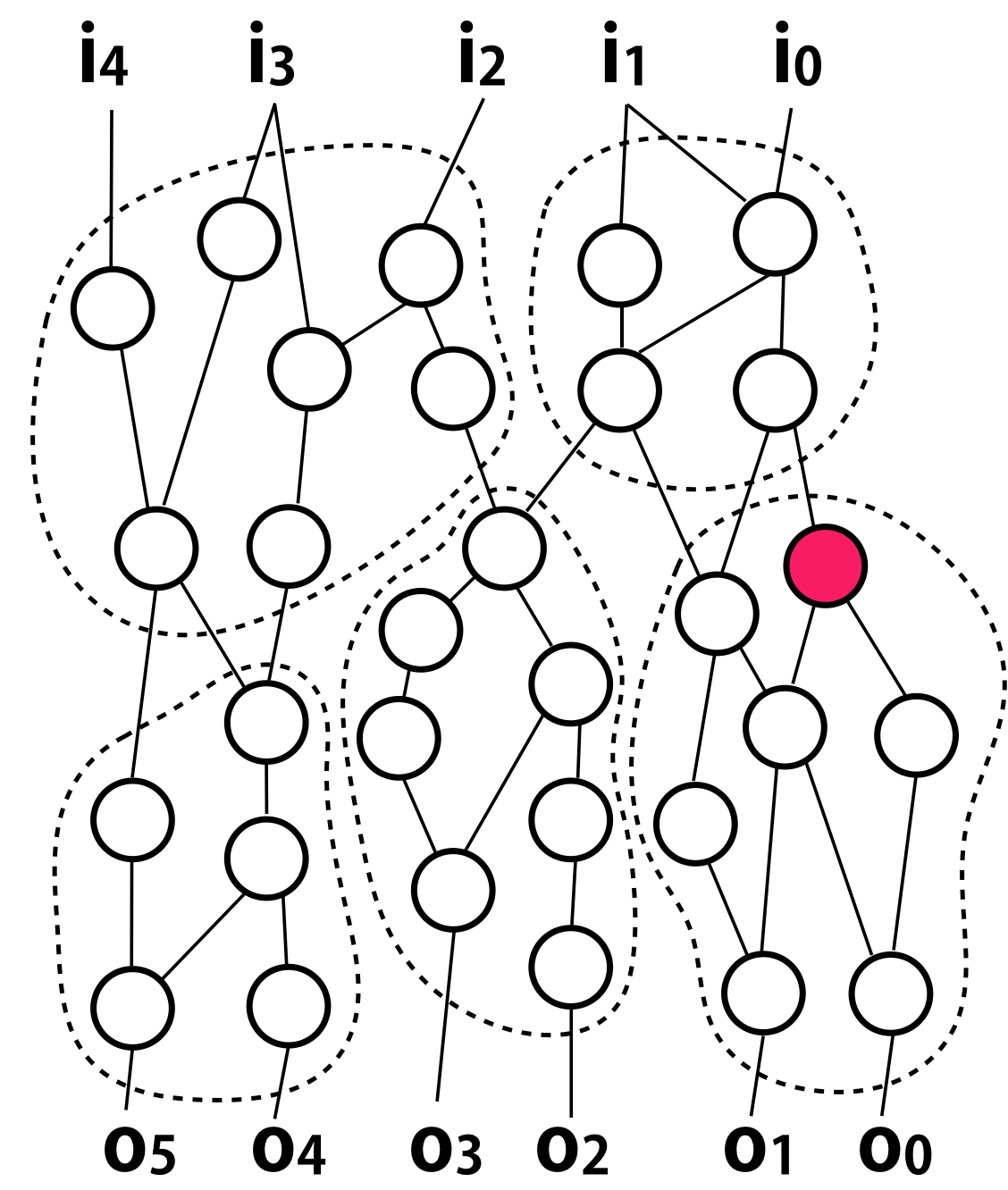

This work aims at deriving an exhaustive circuit error-model, in terms of identification of the influence of each circuit gate (or component) on the final output. The maximum error that can be seen on the circuit primary output if a gate is removed is obtained through a novel partitiong algorithm: by partitioning the original graph representing the circuit into sub-circuits, and by studying each subgraph truth table separately, it is possible to efficiently obtain an accurate estimate of such influence. The novel partitioning algorithm developed exploits the graph topology and monotonicity of subgraphs to improve the result accuracy.

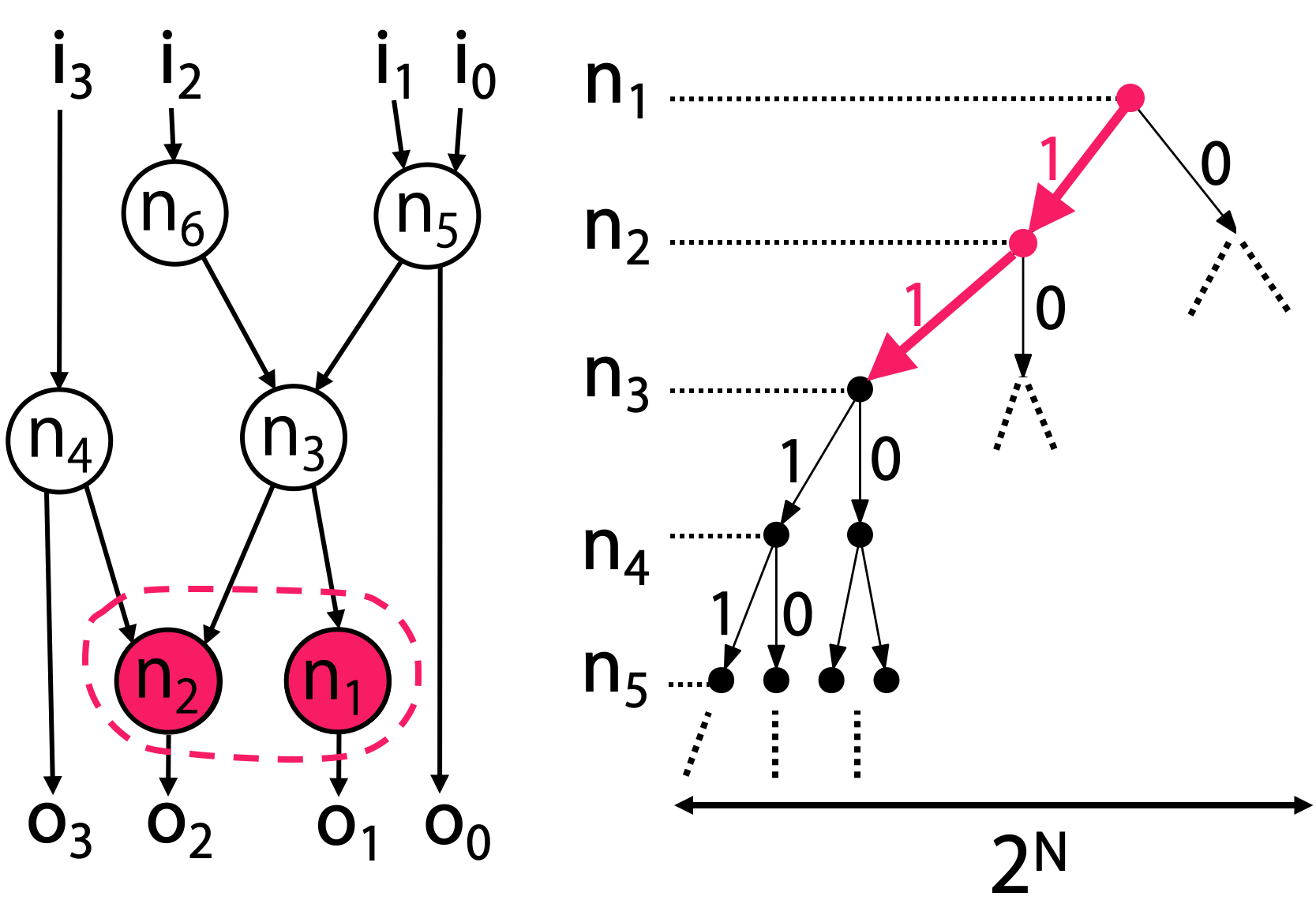

Circuit Carving: A Methodology for the Design of Approximate Hardware

A novel algorithm that aims at synthesising the most efficient circuits given a predefined error threshold, which denotes the maximum tolerated error for that specific application. By considering a circuit netlist, along with the given error threshold, Circuit Carving performs a binary-tree search on the graph nodes to find the maximum subgraph (i.e., subcircuit) that can be eliminated from the circuit without overcoming the abovementioned threshold. Pruning criteria and, in particular, a definition of closure property for subgraphs are exploited to bound the exploration.

Judiciously Spreading Approximation Among Arithmetic Components with Top-Down Inexact Hardware Design

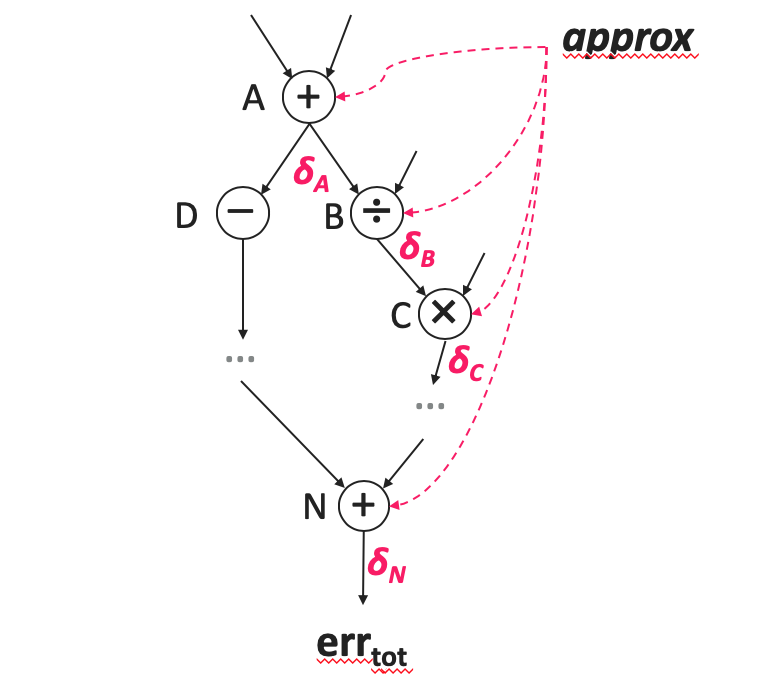

In this work, approximation is applied to data-flow graphs of complex hardware modules, composed of basic arithmetic circuits (adders, multipliers, etc). Starting only from a description of the intended functionality, and a threshold to the overall exactness, this method distributes approximation leeways across the arithmetic operators in a top-down methodology. Error propagation among local approximations is studied, since subsequent operations may magnify it or dampen it.

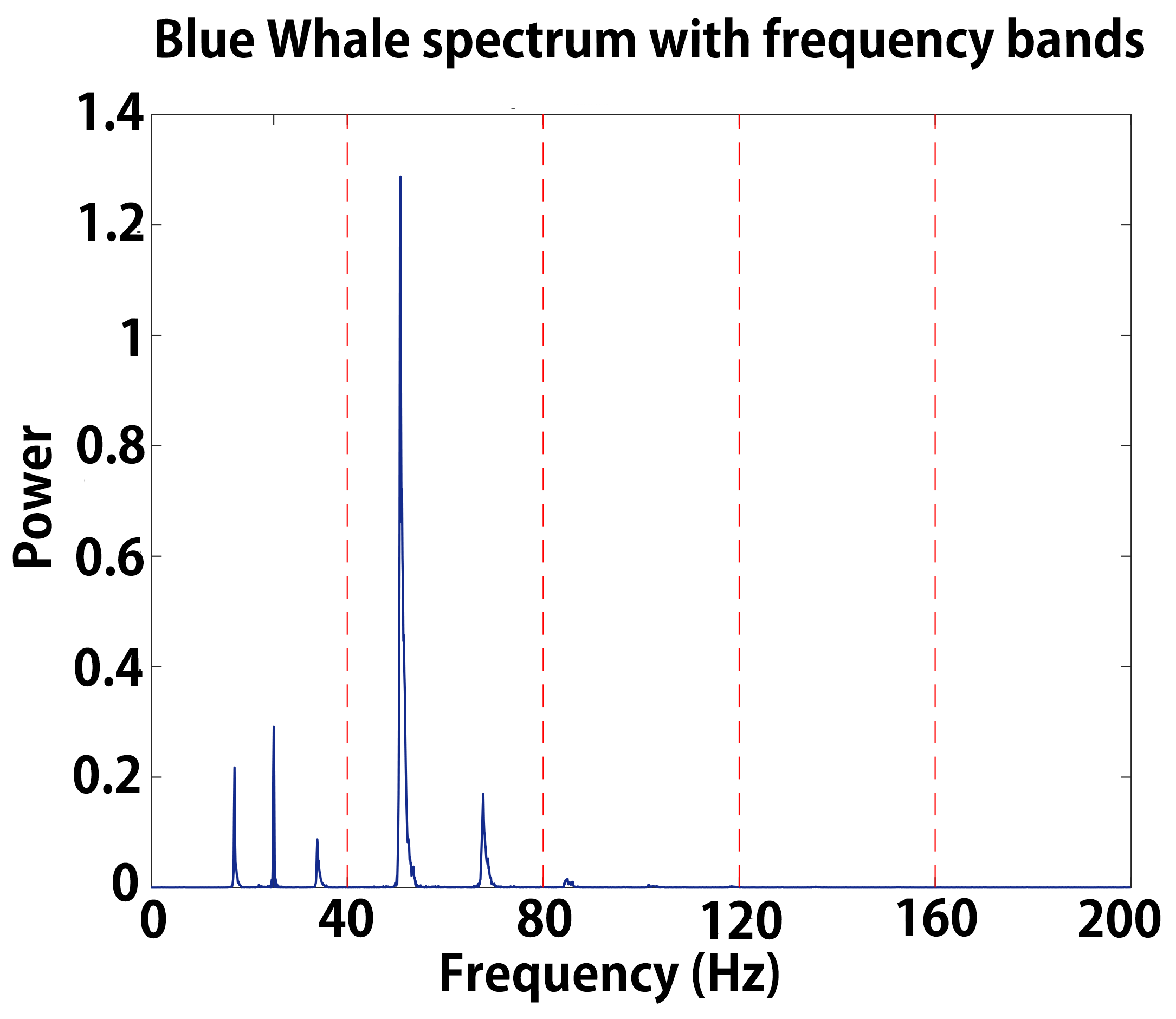

A spectrum-based adaptive sampling algorithm for smart sensing

This work is the subject of my master thesis and presents a novel algorithm based on change-detection tests applied on signal frequency bands to identify anomalies in the signal spectrum and adapt the sampling frequency accordingly. This approach can be employed to monitor changes in a phenomenon observed with wireless sensors, where energy savings are vital for a sustainable infrastructure. A first version of the algorithm has also been tested on programmable boards by STMicroelectronics, confirming its efficiency and validity when exposed to real sensors measuring temperature variations.

Work-in-Progress: A Partitioning Strategy for exploring Error-Resilience in Circuits

Early stage of a more detailed work aimed at finding error-models of circuits through a design-and-conquer approach.

Education

PhD degree at Università della Svizzera italiana, Faculty of Informatics

Supervisor: Prof. Laura Pozzi.

Research area: approximate computing, design of highly efficient approximate hardware.

Visiting PhD student at Imperial College London

Host supervisor: Prof. George A. Constantinides.

Research area: approximate computing, boolean satisfiability for hardware error-modeling, stochastic error propagaton in inexact hardware.

Master degree in Computer Science Engineering at Politecnico di Milano

Thesis: “A spectrum-based adaptive sampling mechanism for energy conservation in Cyber-Physical Systems”. Later published in the IEEE Smartworld 2018 Conference transactions.

Thesis supervisors: Prof. Cesare Alippi, Prof. Manuel Roveri.

Final grade summa cum laude.

Bachelor degree in Mathematical Engineering at Politecnico di Milano

Thesis: “Algorithmics: the spirit of computing”.

Final grade summa cum laude.

Double degree at École Centrale Paris

Double master degree international program T.I.M.E. (Top Industrial Managers for Europe).

Diploma: Scientific high school Alessandro Volta

Final grade: 98/100

Italian winner of EUCYS Contest (European Union Contest for Young Scientists) in fourth year.

Teaching

Computer Architecture

Course resposible: Prof. Marc Langheinrich

Automata and Formal Languages

Course resposible: Prof. Laura Pozzi

Software Atélier: Human-Computer Interaction

Course responsible: dr. M. Landoni

Awards & Grants

- Swiss National Science Foundation grant for Doc.Mobility, 2018

- Politecnico di Milano internal award for brilliant students, from 2010 to 2015

- Italian winner of EUCYS Contest (European Union Contest for Young Scientists), with Clelia Bonardi and Susanna Yi Yu Bai. Realisation of “The Cycloid: a new way of skiing” project, presented to an international jury in Copenhagen for the European final, 2009

- 1st Place - Mathematics Games organised by Centro Pristem of Bocconi University for secondary schools, 2002 and 2003

Academic Activities

I have organized and participated to several events for scientific career-promotion among young girls, strongly believing that soon such events will become unnecessary.-

Celebration of the

International Women and Girls in Science Day at USI Informatics

- L'Ora del Tè con Scienza e Tecnica

- "STEM CAREER TALKS - La scienza? Ma è una cosa da ragazze!" organised by FAST

- "Nuovo Futuro - Ragazze e informatica avanti!" organised by USI