## PROCEEDINGS OF SPIE

# Optical Microlithography XVIII

Bruce W. Smith Chair/Editor

1–4 March 2005 San Jose, California, USA

Sponsored and Published by SPIE—The International Society for Optical Engineering

Cooperating Organization International SEMATECH

> Volume 5754 Part Three of Three Parts

### The Problem of Optimal Placement of Sub-Resolution Assist Features (SRAF)

Maharaj Mukherjee(1), Scott Mansfield(1), Lars Liebmann(1), Alexey Lvov(2), Evanthia Papadopoulou(2), Mark Lavin(2), Zengqin Zhao(1)

Semiconductor Research and Development Center, IBM Microelectronics Division, 2070 Rte 52, Hopewell Junction, NY 12533, USA

(2): Watson Research Lab, IBM Research Division

Route 134, Kitchawan Road, Yorktown Heights, N.Y. 10598, USA

Abstract: In this paper, we present a formulation of the Sub-Resolution Assist Feature (SRAF) placement problem as a geometric optimization problem. We present three independent geometric methodologies that use the above formulation to optimize SRAF placements under mask and lithographic process constraints. Traditional rules-based methodology, are mainly one dimensional in nature. These methods, though apparently very simple, has proven to be inadequate for complex two-dimensional layouts. The methodologies presented in this paper, on the other hand, are inherently two-dimensional and attempt to maximize SRAF coverage on real and complex designs, and minimizes mask rule and lithographic violations.

**Keywords and Phrases:** Resolution Enhancement Techniques (RET), Sub Resolution Assist Features (SRAF), Optical Proximity Correction (OPC), Design Rule Checking (DRC), Mask Rule Checking (MRC), Voronoi Diagram, Geometric Optimization, Lithographic process, Process Window, Simulated Annealing.

#### 1. INTRODUCTION:

1. 1: The problem of SRAF optimization from a geometric perspective:

The continuous advancement of VLSI chip manufacturing technology to meet

Moore's law of shrinking device dimensions in geometric progression has created

ever more new challenges for manufacturing semiconductor chips using optical

microlithography processes. Due to its high volume yield, optical microlithography

appears to remain the method of choice for patterning microelectronic and other

micro-scale chips for the foreseeable future. However, a high yield lithography

process must remain insensitive to variations in exposure dose and focus, and

several Resolution Enhancement Techniques (RET) are being employed to improve

the lithographic process window. Sub-Resolution Assist Features (SRAFs) on

photo-masks is one of the most popular RETs in the deep sub-micron (below 100

nm) lithography technology for increasing the focus tolerance. Usually, SRAFs are

additional rectangular shapes that are placed on masks along the length or the extent of main mask shapes in deep sub-micron lithography [1]. Because of their long thin rectangular shapes, SRAFs are also referred to as Scattering Bars in some literature. SRAFs themselves do not print, but rather help to improve the lithographic process window by increasing the depth of focus of the mask shapes. When adding SRAF to a mask design, assist shapes that have the same tone as the main mask features, shapes that have the opposite tone as the main mask features or assist shapes of both tones may be utilized. In any case, a main mask shape that has an SRAF in its close vicinity is referred to as being covered, or assisted, by the SRAF and, generally, has a much better focus tolerance than mask shapes that are not covered by an SRAF.

The SRAF coverage of the primary shapes is often limited by the complex mask manufacturing constraints and the lithographic process constraints [2]. In addition, the application of Optical Proximity Correction (OPC) on the main shapes creates more complex mask manufacturing constraints for the SRAFs. In a rules-based methodology, SRAF placement is optimized by maximizing the focus window and minimizing the likelihood of SRAF printing for one-dimensional main features [3, 4]. The problem becomes more complex with real mask designs because of the twodimensional and complex interaction of primary features and SRAFs. Rules derived from one-dimensional features cannot provide adequate SRAF coverage under increased spatial frequency of edges of the primary mask features. Often the satisfaction of mask manufacturability constraints is enforced by cleaning up SRAFs that violate these constraints. This removal of SRAF leaves unassisted main features with inadequate process window for proper yield of the circuit [5].

In this paper, we present a set of methodologies for optimizing SRAF coverage on real, two-dimensional designs that consider the geometric placements of primary mask features. These methodologies optimize SRAF placements under mask manufacturing and lithographic process constraints, while optimizing the SRAF coverage of main features. The resulting SRAF placements from these methodologies violate fewer mask manufacturability constraints. As a result, fewer SRAF get removed during the SRAF cleanup processes, maximizing the SRAF coverage for the main features of the layout.

#### 1.2: Current limitations of the SRAF placements and its effects on the process window:

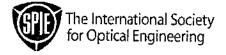

The current SRAF placement methodology still broadly follows a rules based methodology as described in Figure 1. A good description of the current methodology can be found in [6], which is described briefly here. The primary rules for the SRAF placement are derived experimentally for various pitches. The rules describe whether a particular pitch needs an SRAF or not. If the pitch requires an SRAF, then the rules describe the spacing and the width of the SRAF. Some pitches

may require multiple SRAF and in that case, the spacing between two consecutive SRAFs is also described in the rule.

Figure 1: Flow Diagram of SRAF placement and cleaning using one-dimensional rules.

The integration of the one dimensional rule in the two dimensional environment of a mask layout creates a lot of challenges. Previously these two dimensional scenarios were handled by still more rules which are generally referred to as style options [5]. The style options, as defined in this paper, are very broad based and consider both mask effects and the lithographic effects. However, this paper does not describe how to clearly identify and demarcate two-dimensional regions. We describe a methodology in this paper using Voronoi Diagrams, where two dimensional regions can be clearly defined. Both the one dimensional placement of SRAF and their two dimensional interactions are affected by the mask manufacturing constraints and the possibility of SRAF-printing. The style options usually take a very conservative approach and eliminate the SRAF wherever there is either a violation of the mask manufacturing constraints or there is a likely hood of SRAF printing. This is also described in Figure 1. The problem gets more complicated where both clear and opaque tone SRAFs are used. In this paper, we

describe a comprehensive methodology that integrates the one dimensional SRAF generation rules with two dimensional SRAF placements for a mask layout.

#### 2. DESCRIPTION OF OUR WORK

## 2.1 SRAF placement from an optimization perspective:

We formalize the SRAF placement problem as a geometric optimization problem involving both the main mask features and the SRAFs. The objective function of the optimization problem is defined as the total extent of edges of the main features that are *assisted* or, in other words, have at least one SRAF in their close vicinity. The constraints of the optimization problem for SRAF placement are a set of mask manufacturability constraints and a set of lithographic process constraints.

The set of mask manufacturability constraints require that the SRAF can be manufactured by the mask process. Examples of some of the mask manufacturability constraints are the minimum width and length of an SRAF and its aspect ratio. Other examples of mask manufacturability constraints are the minimum distance between two SRAFs; the minimum distance between an SRAF and a main feature shape; and the minimum corner-to-corner distances between two SRAFs. Similar constraints exist between an SRAF and a main feature shape. The lithographic process constraints mainly deal with the requirements that SRAFs do not print under any circumstances. Since a variation of the dose can make an SRAF print, the dose window may shrink if the lithographic constraint is not chosen carefully. In order to prevent any portions of an SRAF from printing, special attention must be given where two SRAF would cross or meet with each other. The SRAF generation rules are obtained by assuming the one-dimensional conditions. The width, the distance from the main shape, the distance from inward corners and some other parameters of SRAFs depend on a particular lithography process. These parameters are defined once either by a simulation program or experimentally.

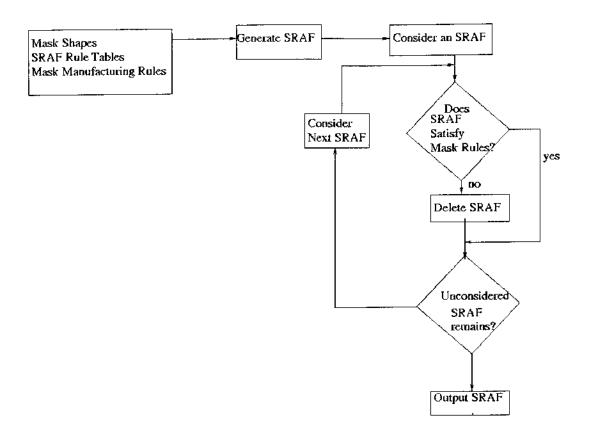

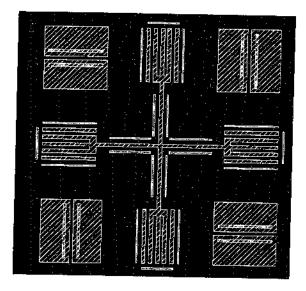

Figure 2: A method of optimizing SRAF using Simulated Annealing. The method generates several configurations of SRAF under mask manufacturing constraints and chooses the one that optimizes the process window.

Usually in the rule based SRAF placement methodology, the placement rules are set by maximizing the focus window and minimizing the likelihood of SRAF printing for long parallel rectangles, or *one-dimensional* features. The problem becomes more complex when mask features become complex and they interact with each other. The increase of shape complexity in the mask increases the spatial frequency (number of small jogs per nm) of their edges. This in turn brings increased variations in SRAF placements. The rules based mainly on one-dimensional features cannot adequately handle the SRAF placement under increased spatial frequency of shape edges. The problem is exacerbated by the tight mask manufacturability and non-printability requirements. Often the satisfaction of mask manufacturability constraints is enforced by cleaning up any violations of constraints. The resulting SRAF placement often has many uncovered main features. This reduces the process window below what is required for proper yield of the circuit.

In the following three sections we describe three independent methodologies to optimize SRAF placements. In Section 2.2, we describe an SRAF placement that optimizes the process window using Simulated Annealing. In the Section 2.3, we use a smoothing operator on the primary features to reduce spatial frequency before placement of SRAFs. In section 2.4, we use Voronoi diagram of the primary features for the optimal placement of SRAFs.

2.2 Use of Simulated Annealing for Optimal SRAF placements:

We have tried Simulated Annealing for obtaining the best SRAF placement to optimize the process window for simple two dimensional structures. An example of SRAF placement using Simulated Annealing is shown in Figure 2. This program is created at the IBM T. J. Watson Research Lab. Simulated annealing is an optimization methodology that is used in many applications related to Electronic Design Automation (EDA). The methodology allows optimizing an objective function with a given cooling schedule. The slower the cooling schedule the closer is the generated result to the global optima. In our program, we generate several SRAF placements for a given mask feature and the set of mask manufacturing constraints. In Figure 2, we show several mask structures and the generated SRAFs and the corresponding wafer images.

2.3 Use of smoothing on the primary mask shapes:

As we have explained in the previous sections, the one-dimensional SRAF rules do not integrate well within the two dimensional mask features for real layouts. The increased presence of two dimensional mask features can be described in terms of the increased spatial frequency of the primary mask features and layouts with higher spatial frequencies are more likely to have some main features remain uncovered due to SRAF cleanup. One way, therefore, to increase SRAF coverage is to reduce the spatial frequency of the primary mask features. To optimize the SRAF coverage, we increase the uniformity of the SRAF placement by the application of smoothing on the primary mask shapes. The increased smoothness of the edges of the primary mask shapes result in uniformity of the SRAF placement. The resulting uniform SRAF placement violates fewer mask manufacturability constraints and diminishes any likelihood of their removal during any cleaning up in a later stage. This methodology optimizes the number of edges of main features having SRAF in their vicinity. The resulting SRAF placements extend the coverage of mask shapes and increase the focus window. This method is explained by the set of figures below.

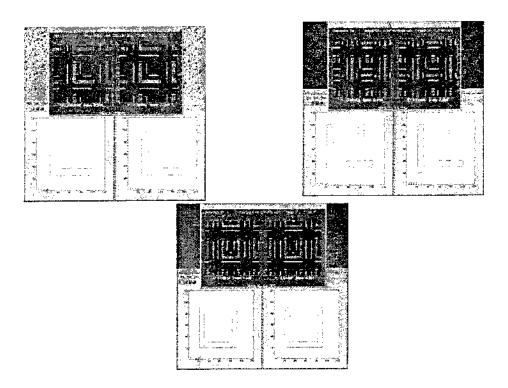

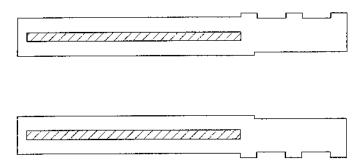

In Figure 3, we present a reverse-tone SRAF placement (holes within the main features) based on one dimensional rule only without application of any constraints. This shows as the SRAF should be before cleaning up any mask rule violations.

Figure 3: A reverse-tone SRAF placement using one-dimensional rules prior to cleanup for satisfying mask manufacturing rules.

In the Figure 4, we show the SRAF placement after cleaning up all the mask manufacturability constraints and lithographic process constraints violations (in particular SRAFs can not cross or have jogs). Evidently, there are some regions of the main features with high spatial frequency of edges that are not covered by SRAF.

Figure 4: The SRAF placements as shown in Figure 3, after cleaning up all violations of mask manufacturing and lithographic process constraints.

In Figure 5, we show how our methodology improves the SRAF placement by presmoothing the main features.

Figure 5: Application of smoothing to main features reduces the variations and jogs in the SRAF placement. The cleanup following the initial placement removes fewer SRAFs and increases the SRAF coverage.

The smoothing of the main shapes in our methodology is used only as guidance for the placement of SRAFs. The smoothing does not affect application of any other RETs or the Optical Proximity Correction (OPC). When applied to our process, our methodology improves the SRAF placement both qualitatively and quantitatively. Fewer SRAFs are generated, yet the coverage improves by having longer SRAFs. Having less, more-uniform SRAF also helps to improve runtime of any further RET and OPC operations.

This methodology can be used for placement of SRAFs of either reverse or same tone. In Figure 6, we show a placement of SRAFs of both tones using the above methodology.

Figure 6: Smoothing of main shapes allow optimal placement of SRAFs of both tones.

## 2.4 Optimized placement of SRAF by using the Voronoi Diagram:

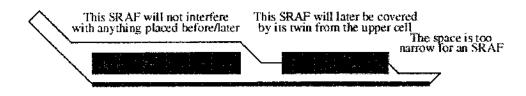

The Voronoi Diagram method is aimed at not just resolving, but actually preventing, two dimensional SRAF placement conflicts. For example in Figure 7, we show a simple situation where there are possible conflicts in the SRAF placements. A simple Voronoi diagram can identify these conflicts.

1 dimensional rules: SRAFs are simply placed parallel to the edges at a fixed distance.

1 dimensional rules: After the mask rules enforcement two SRAFs are 'cleaned up'.

Voronoi Diagram method: The mask rules are satisfied, All four SRAFs are present. The total length of the assisted edges is greater than in 2).

**Figure 7:** The Voronoi diagram attempts to identify two dimensional SRAF conflicts.

The Voronoi diagram of a set of shapes  $S = \{S_1, S_2, ..., S_n\}$  in respect to some metric M is the partition of the plane into n regions  $V_1, V_2, ..., V_n$ , one for each shape of S, boundary B. Each Voronoi cell  $V_i$  is uniquely defined by the property: The M-distance from any point p of  $V_i$  to the shape  $S_i$  is strictly less then the M-distance from p to any other shape  $V_j$ ,  $J^{\neq J}$ .

The method of placing the SRAFs using Voronoi diagram is summarized as:

- 1) Our metric M is what is typically called the  $L_{\infty}$  metric: The  $L_{\infty}$  distance between two points  $p = (p_x, p_y), q = (q_x, q_y)$  is

- $d_{\infty}(p,q) = \max\{|p_x p_y|, |q_x q_y|\}$ . The  $L_{\infty}$  metric is similar to the well known

Manhattan metric under 45-degree rotation. We use the  $L_{\infty}$  metric because it considerably simplifies the construction of the Voronoi diagram and it is very appropriate for VLSI shapes whose edges are in their majority axis-parallel (see [7, 8] for more details).

- Our Voronoi shapes are the edges of the primary shapes. That is  $S_1$ ,  $S_2$ , ...,  $S_n$  are segments.

- 3) We build the Voronoi diagram. Each edge of each primary shape now has a Voronoi cell associated with it. Each Voronoi edge is simply the bisector between two elements of primary shapes. In the  $L_{\infty}$  metric there may be areas equidistant from two collinear edges of the primary shapes as the areas shown shaded in Figure

.7

8. Equidistant regions are assigned arbitrarily to one of the involved primary shapes. For details on the properties of the  $L_{\infty}$  Voronoi diagram of VLSI shapes see [7]. The following figure shows an example:

Figure 8: Example of a Voronoi diagram construct for a set of rectangles using the  $L_{\infty}$  - Metric.

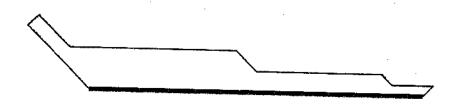

A single Voronoi cell looks like this:

Figure 9: A typical Voronoi cell with  $L_{\infty}$  - Metric.

4) Consider each Voronoi cell separately and independently of the others. The main statement of the Voronoi SRAF placement method is: Given an edge of a primary shape, the SRAFs can be placed based solely on the shape of the

corresponding Voronoi cell and according to some 'smart' set of rules. We do not describe this set of rules in detail, but only mention some main properties:

- Every SRAF is a rectangle.

- Every SRAF is placed either completely inside of the Voronoi cell or on the boundary of the Voronoi cell.

- After all SRAFs for all cells are placed, any two SRAFs either do not intersect or completely coincide.

For example the SRAF placement for a typical Voronoi cell of Figure 9 is shown in Figure 10.

Figure 10: SRAF placements within the Voronoi cell of Figure 8.

The Voronoi method runtime is O(nlog(n)) + O(n), where n is the number of the primary shape edges and O(nlog(n)) is the time to construct the Voronoi diagram in the  $L_{\infty}$  metric. The algorithm is based on plane sweep and is described in detail in [7, 8, 9].

VLSI shapes are in their vast majority axis-parallel; therefore, the  $L_{\infty}$  Voronoi diagram is a simple and practical structure. For example, if shapes are strictly axis-parallel, the Voronoi diagram consists solely of axis-parallel line segments and line segments of slope +1 or -1. If shapes also contain 45-degree segments, the Voronoi diagram remains a structure of line segments in only 8 orientations. These are typical cases of VLSI layouts where the construction of the  $L_{\infty}$  Voronoi diagram is extremely simplified. Due to this simplicity, the  $L_{\infty}$  Voronoi diagram has been developed and used by IBMicroelectronics for a different application, in particular, critical area estimation and the prediction of yield [9]. We based our Voronoi SRAF tool on the IBM Voronoi diagram code available in that tool.

The principle of the Voronoi diagram, specifically identification of the regions which are closer to a certain edge than to any other edge, perfectly matches our goal to place the assist features so that the each assist feature assists its own edge and minimally interacts with the other SRAFs and edges. Since the diagram itself can be built quite rapidly, the above method turns out to be an excellent vehicle for placing SRAFs and, in particular, for resolving crossing SRAFs conflicts.

One alternative method would be to place all SRAFs ignoring intersections, and then 'clean up' some of the SRAFs or their parts which cause crossings. The fatal

drawback of this method is that often if we throw away a part of an SRAF, the remaining part starts to violate the minimum size manufacturability requirement. We then have to remove it as well and , thus, remove the whole SRAF. This leads to about 50% loss in total SRAF coverage.

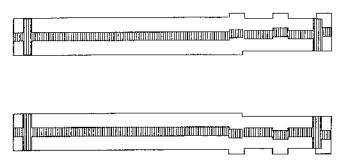

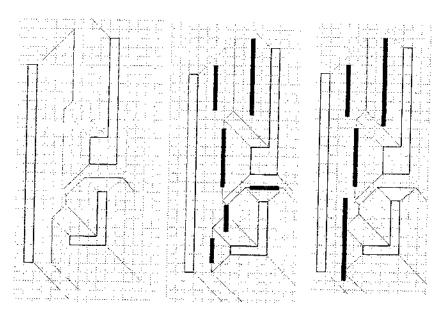

The Voronoi diagram SRAF placement algorithm was implemented in C++ at IBM T.J.Watson Research Lab in 2003. A comparison of a real design layout using SRAF generated using the standard rules based approach and the Voronoi approach is shown in Figure 11. Here the the left most figure shows part of the layout. The middle figure shows SRAF placement using traditional rule-based methods, The figure on the right shows SRAF placement by using Voronoi diagram. Note the additional SRAF coverage by using the later method.

Figure 11: SRAF placements for a real layout using Voronoi Diagram.

#### 3. SUMMARY AND CONCLUSION

In this paper, we have presented a formalization of the SRAF placement problem as a geometric optimization problem. We demonstrated the usefulness of the formulation by presenting a few methodologies for optimizing SRAF placements. The results of these methodologies tend to better integrate the one dimensional rules in the two dimensional mask layouts. These methods would work for SRAFs of either reverse or same tones or both. The optimization problem works out better than additional rules that are often put in place for resolving two dimensional conflicts.

#### 4. REFERENCES:

- 1. L. Liebmann and S. Mansfield, "Method of incorporating sub resolution assist features in a photomask layout", US Patent 6413683, 2002.

- 2. J. Bruce, M. Cross, L. Liebmann, S. Mansfield, and A. McGuire, "Assist Features Challenges and Opportunities", ARCH Microlithography Symp., 2000

- 3. S. Mansfield, L. Liebmann, A. Molless and A. K. Wong, "Lithographic Comparison of Assist Feature Design Strategies", in Proc. SPIE, vol. 4000, 2000.

- 4. J. F. Chen, K. Wampler and T. L. Laidig, "Optical proximity correction methods for intermediate pitch features using sub-resolution scattering bars on a mask", US Patent 5821014, 1998.

- 5. L. Liebmann, J. A. Bruce, W Chu, M. Cross, I. Graur, J. Crueger, W. Leipold, S. Mansfield, A. McGuire, and D. Sundling, "Optimizing style options for sub-resolution assist features", in Proc. SPIE, vol. 4346, 2001

- 6. S. Mansfield, L. Liebmann, S. Butt, and H. Haffner, "Semiconductor device fabrication using a photomask with assist features" US Patent 6421820, 2003.

- 7. "Critical Area Computation via Voronoi diagrams", E. Papadopoulou and D.T. Lee, *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 18, No. 4, April 1999, 463-474.

- 8. "The  $L\infty$  Voronoi Diagram of Segments and VLSI Applications", E. Papadopoulou and D.T. Lee, *International Journal of Computational Geometry and Applications*, vol. 11, No. 5, 2001, 503-528.

- 9. "CAE: Critical Area Extraction", Internal IBM tool for the prediction of yield of VLSI chips, Department of Electronic Design Automation, IBM Microelectronics Division, Burlington, VT. Initial patents: US 6178539, US 6317859.